RESEARCH

Nanoscale Silver Paste and Its Low-temperature Sintering for Chip Attachment (2004)

Having led the way of banning lead (Pb) in electronic products, European electronic manufacturers, particularly some major power electronics companies in Germany, are aggressively implementing a silver sintering technology for interconnecting semiconductor chips. Semikron, Europe's market leader in power modules recently announced a parallel manufacturing line for making power modules using low-temperature sintering of thick-film silver pastes for joining power chips. With the sintered chip-attachment, Semikron claimed to achieve 3x better performance, 5x better reliability, and higher chip junction temperature up to 175°C. However, a serious drawback of Semikron's sintering technology is the requirement of high quasi-static pressure (> 40 MPa) to lower the sintering temperature of thick-film silver pastes to about 250°C. The need of large pressure complicates the manufacturing process and places critical demands on substrate flatness and chip thickness.

We followed a strategy of using nanoparticles of silver to lower its sintering temperature with low or no pressure. From the science of sintering, driving force for densification of a particle compact increases with decreasing particle size, thus the densification rate - a product of thermodynamic driving force and kinetics - could still be high at low temperatures even with low atomic diffusion rate. We formulated a uniform silver paste containing 30-nm silver particles. Uniform "green" microstructure of the paste is evident from images taken in a scanning electron microscope. The paste viscosity can be adjusted for screen/stencil printing or dispensing.

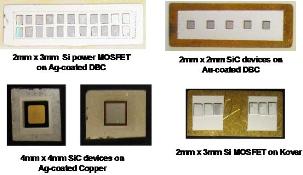

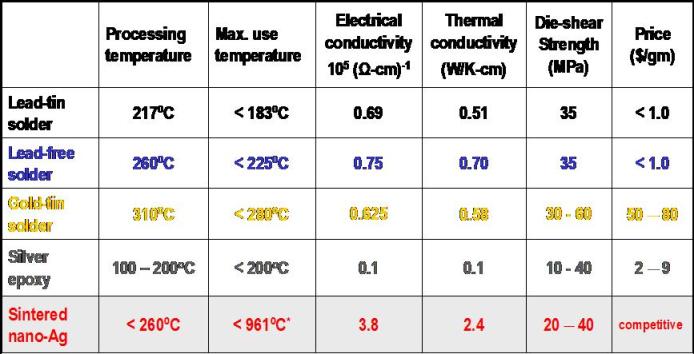

The top figure shows the flow chart for making and applying the nanosilver paste. Examples of some sintered power chips on various substrates are shown in the bottom figure. Table below lists key features of the nanosilver paste versus some existing attachment materials. The sintered attachment clearly has excellent electrical, thermal, mechanical, and thermo-mechanical properties and offers a simpler, lead-free solution for chip interconnection than the European technology.